一、什么是chipwatcher

在编程开发过程的调试阶段,可以借助一些编译环境集成的工具帮助我们更好地定位疑问。当我们完成一份工程代【dài】码但是观测不到我们想要的结果时,我们需要进一步确认是哪部分的代码出现了偏差【chà】导致得不到我们想要的结果。

对于MCU来说,我们可以借助JLINK仿真器来实现断点测试,进而监视每一步的数【shù】据变化,从而定位到疑问所在;对于FPGA而言,想要监视内部信号的【de】变化,也【yě】有对应的工具可以使用。

这些工具,不同的芯【xīn】片厂商根据自家的编译环境集成了他们各自的工具,例如,Xilinx ISE的chipscope,altera quartus II 的SignalProbe等。本文中安路TD的chipwatcher也是用于观测电路内部信号变化的工具,可以认为这是一款【kuǎn】相似于逻辑分【fèn】析仪的工【gōng】具,只不过观测的信号不是芯片引脚上面的信号,而是电路内部的信号。

当我们需要定【dìng】位疑问的时候,可以在工具中添加我们想要查看的信号,通过【guò】抓取波形来确认信号是否在根据我们的需求进行变化。

二、Chipwatcher使用流程

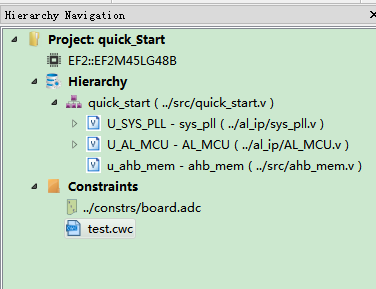

首先,一个FPGA工程常见的构成如下:

1. 功能代码文件:后缀为.v的文件,通俗地讲就是我们自己写的代码。

2. 例化的IP文件【jiàn】:通过编译软件来例化的IP的【de】代码,不同厂商例化后的IP文件名后缀有差异,安路的TD中直接将例化完毕后的.v文件加入工程即可。这类文件不是必须的,有用到需要的IP就加,没有不加【jiā】。

3. IO约束文件:用来定义整个工程的输入输出信号【hào】对应的具体芯片引脚是哪个。这类文件可【kě】以不加,不加的话编译工具会自动分配IO口。

4. 时钟约束文件:即SDC文件。同IO约束文件,不加的话编译器会【huì】自己约束,因此当工程较大时序较为复杂时通常需要我们自己约束。

以上四种文件通过编译后一起生成的整个工程的bit文件烧录进FPGA芯片后,假设代码功能正常,则芯片【piàn】开始【shǐ】工作。

假设功能不正常,当我们想要监视电路内部信号的时候,我们还需要在工程中加入另一类文件,即第五类文件,然后将这五类文件【jiàn】统一打包成【chéng】bit文件后下载进FPGA,此时才【cái】可以利用工具观测和抓取到我们想看的信号。

这第五类文件,在TD中,即为Chipwatcher工具生成的.cwc文件。

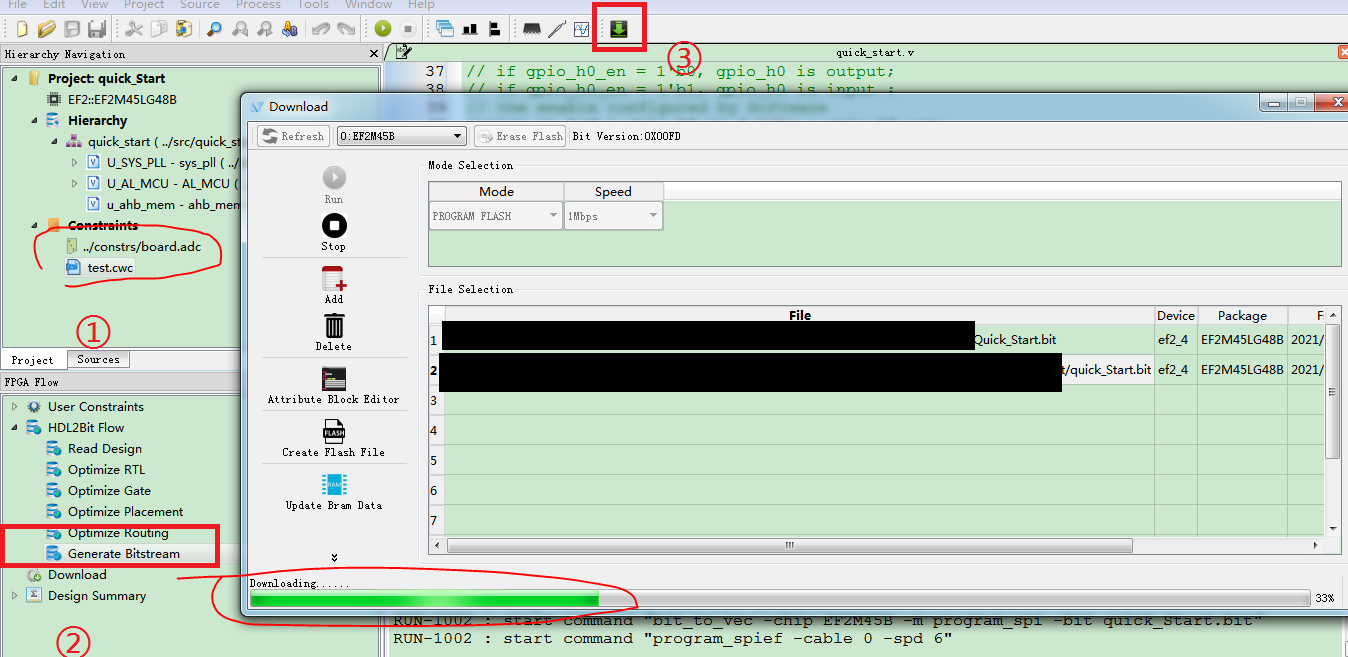

下图展【zhǎn】示了一个加入【rù】.cwc文件后的工程目录(该工程中未加入时序约束文件):

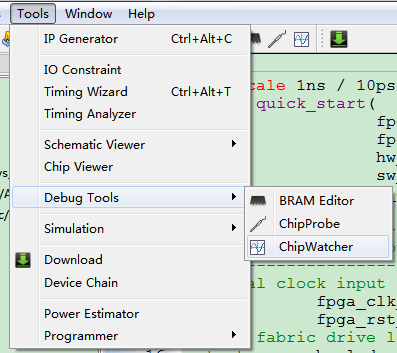

生成cwc文件的过程如下:

Tools -> Debug Tools -> chipwatcher

进入到chipwatcher页面:

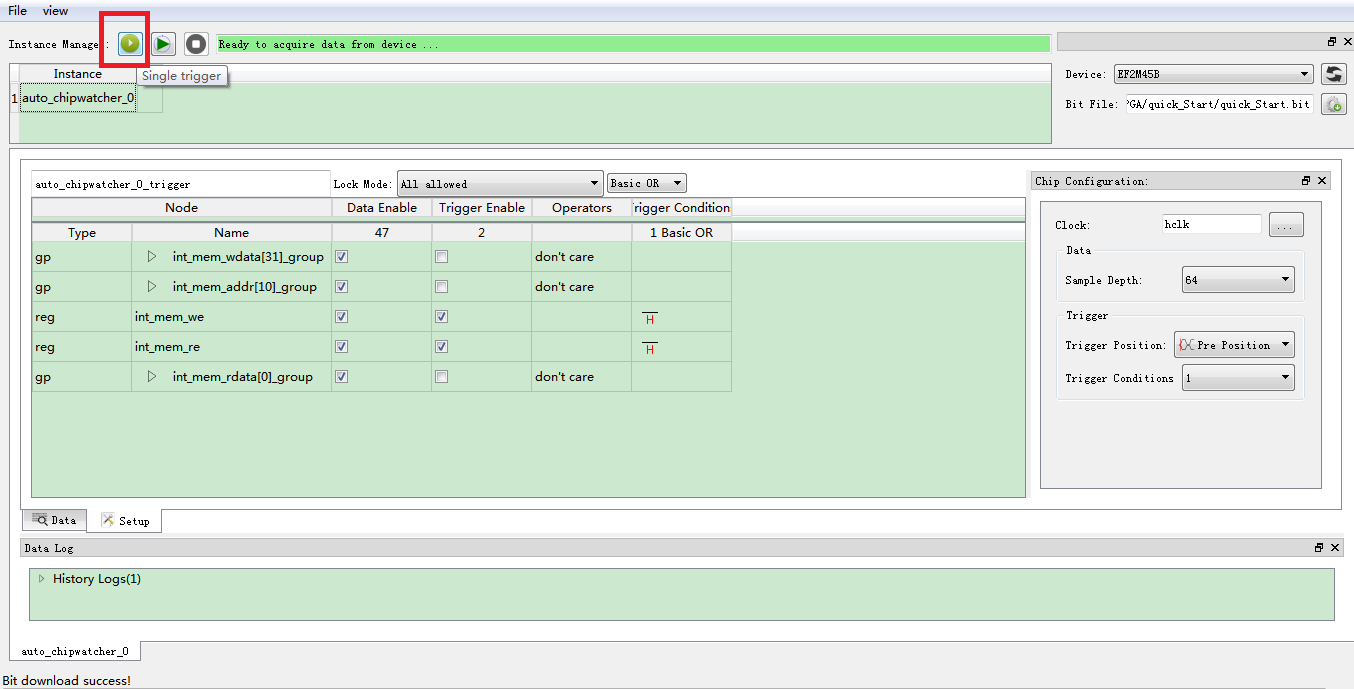

如上图,①区是【shì】选择采样时钟和采样深度,采样时钟的选择注意要选择全局时钟中频率最高的时钟,采样深度越深(即数值越大),最终生成的bit文件所占用的芯片资源越多。

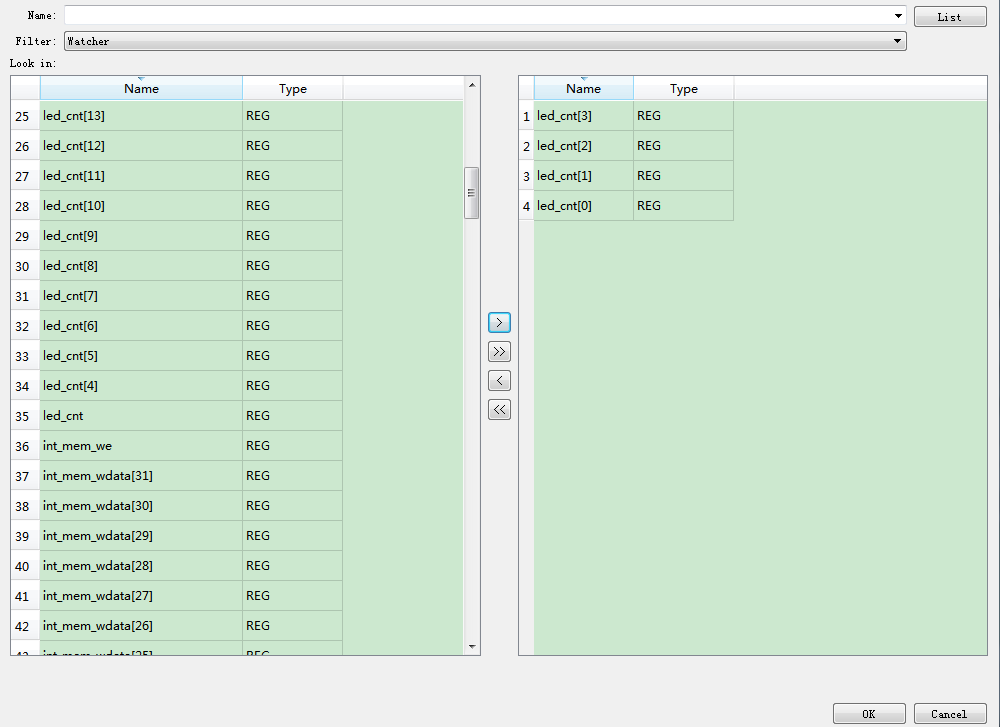

②区是添加想监视的信号的【de】区域,添加方法:在该区域右键后,选择add nodes进入【rù】到信号选择的页面,如下:

如图可以选择想要监视的信号至右侧,全部选择完毕后,点击OK即可。

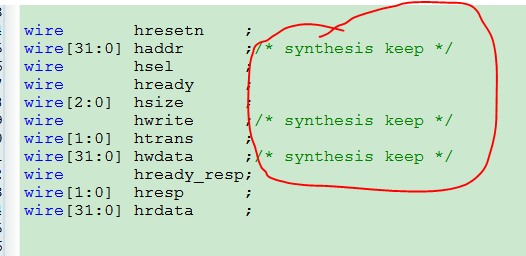

需要注意的是,有些信号会自动被编译器优化,而在list中不被显示,此时若是想观测对应的信号,可以回到我们的代码中加上如下【xià】关键词即【jí】可:

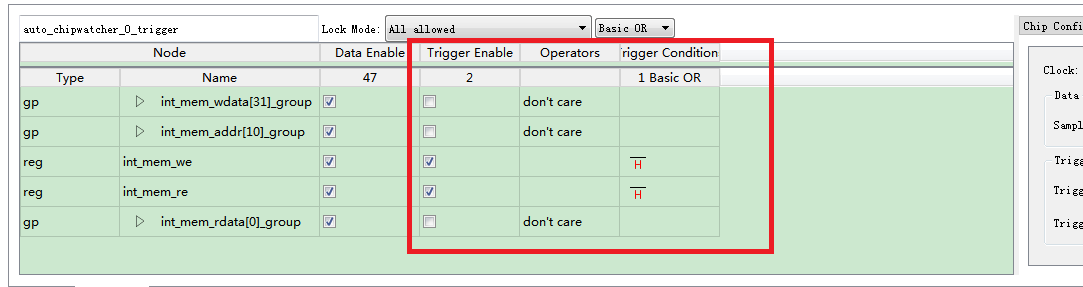

添加完想要监视的信号后,设置触发条件。

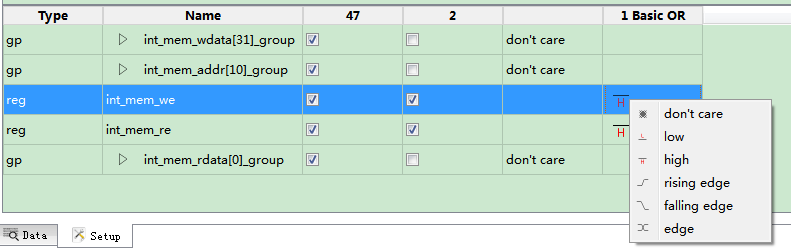

如图,在trigger enable栏选择触发信号,在rigger condition栏选择触发条件(右键)

触发条件共有以下几种:

分别表示低电平触发、高电平触发、上升沿触发、下降沿触发和边沿触发。

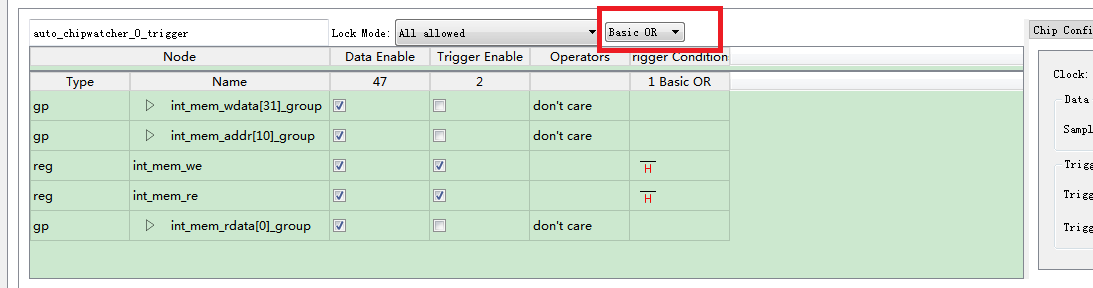

在如上图处设置触发信号之间的关系。图中设置为或【huò】,即只要其中一个信号满【mǎn】足条件即可。

上图中的整体触发条件设置完毕后可叙述为:当int_mem_we信号或int_mem_re信号其中【zhōng】之一【yī】为高电平时,抓取当前int_mem_wdata[31 :0]、int_mem_addr[10 :0]、int_mem_rdata[31 :0]、int_mem_we和int_mem_re的波形。

编辑完毕后即可保存文件。

保存后生成对应的cwc文件,同时将文件加入工程,最后编译下载至开发板。

(注释:①为将生成的cwc文件加入工程,②为编译【yì】工程,③为将bit文件下载至开发【fā】板)

下载成功后,返回chipwatcher设置页面,如下图选择single trigger,即单次触发。

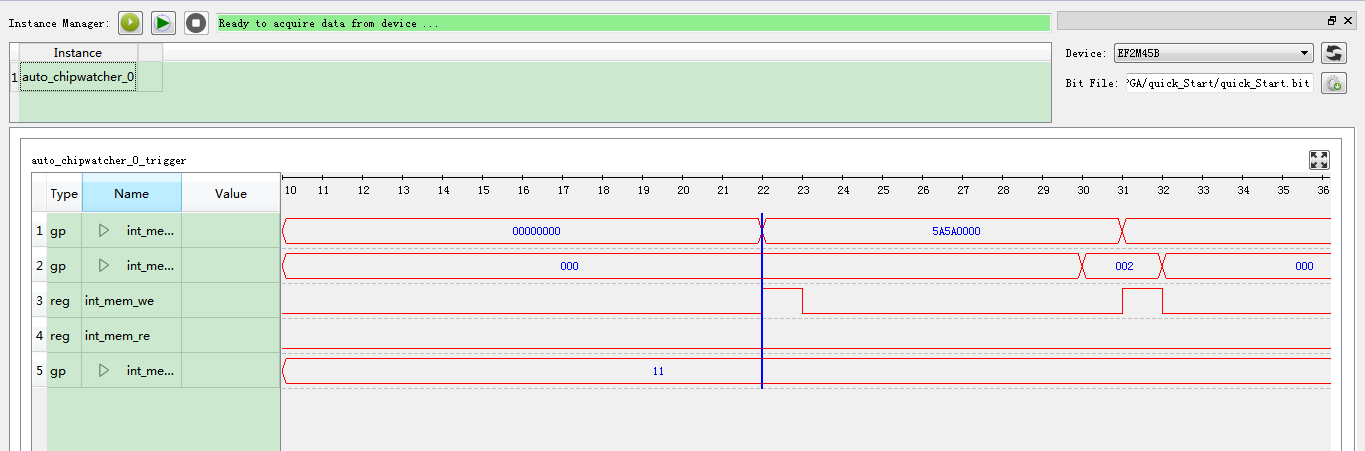

当程序运行并满足触发条件时,chipwatcher会抓取到波形,如下:

三、FPGA调试与MCU调试的一些思路差异

Chipwatcher的调试过程大体如第二章中所示,但是很长一段时间【jiān】段,我并没有在chipwatcher中监视到任何波形,究其原因是没有从MCU调试的思维转变过来。

MCU的断点调试,可以认为是一步一【yī】步【bù】执行的,没有点击下一步之前,程序会一直停留在当前位置(除非程序跑飞)。

而FPGA调试没有这种机制,当bit文件下【xià】载至芯片后,程序是一直执行的,而点击single trigger后只不过是当满足触【chù】发条件时抓取当【dāng】前波形而已。抓取完毕会显示波形,程序却依旧在继续执行,不会停留在抓取完毕的那一刻。

当我【wǒ】使用chipwatcher监视【shì】AHB协议传输时,没有在数据线和地址线上面监视到波形就是没有意识到这点。在bit文件下载进芯片时传输就已经开始了(对比MCU的调试,通常MCU调试开始时,环境一般会在main函数起始自【zì】动设置断点),假设传输在我开【kāi】启触发按键前就已经完成,则传输线上就会一直监视不到数据,触发条【tiáo】件也会一直不成立。

因此,为了确保能够顺利抓取到传输的数据,需要在传输前设置相应的延时,保证当点击single trigger,chipwatcher开始根据设置的触【chù】发【fā】条件抓取波形时,数据的传输【shū】还没有开始。

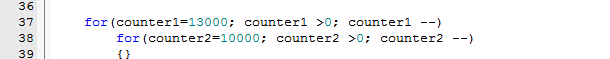

例程是MCU和FPGA根据AHB协【xié】议进行通信,因此后来我在MCU的工程中添【tiān】加了一段延时:

确保留出充足的时间段来操作chipwatcher。

返回列表